No VCD file is generated.

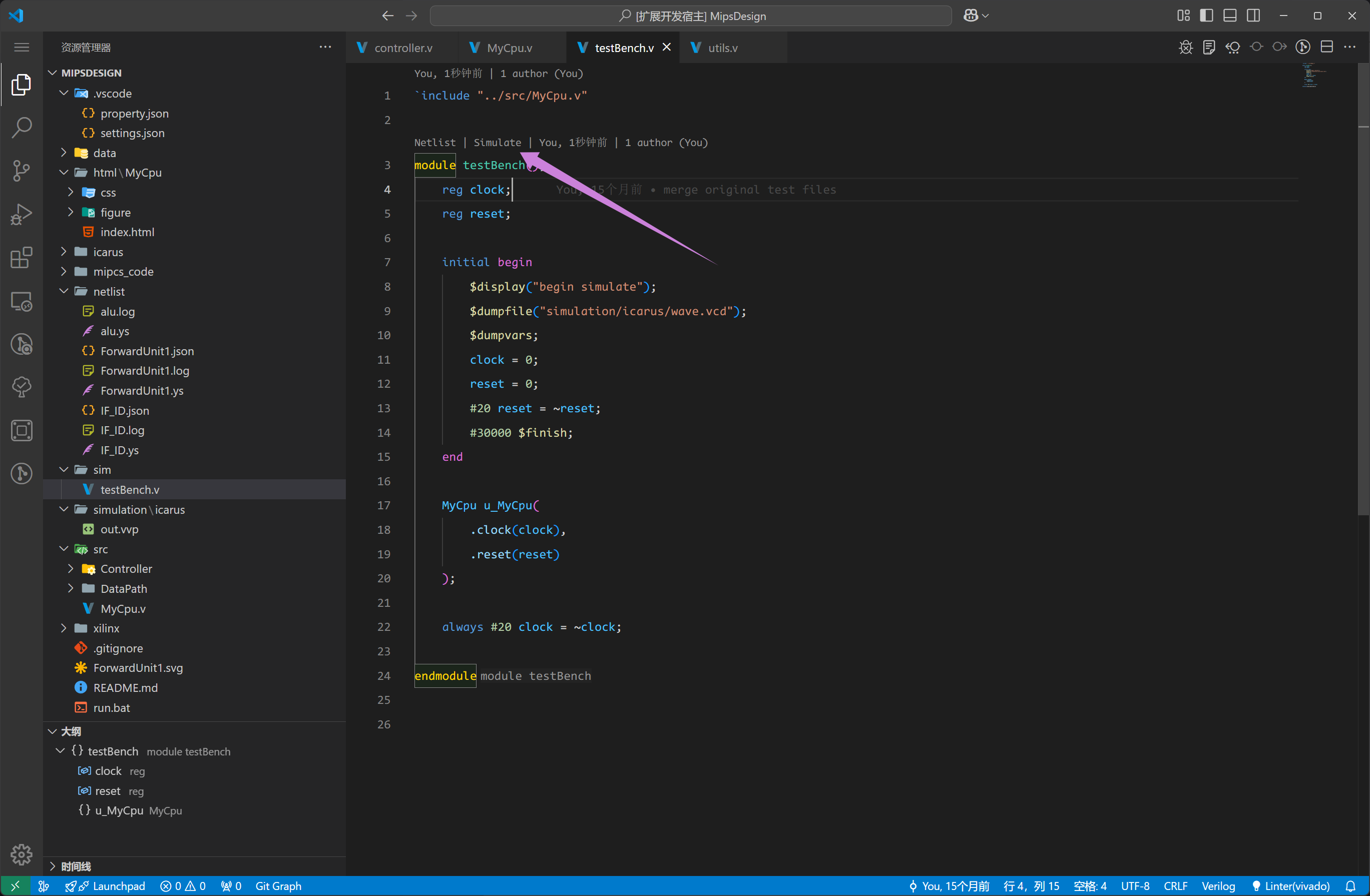

If no errors occurred during execution, the issue might be that the testbench (TB) file is missing statements to generate the VCD waveform file:

initial begin

$dumpfile("prj/icarus/FFT_IFFT.vcd");

$dumpvars(0, FFT_IFFT_tb);

#2000 $finish();

end