没有生成 vcd 文件

如果运行的过程中没有报错,那可能是tb文件中缺少生成vcd波形文件的语句:

initial begin

$dumpfile("prj/icarus/FFT_IFFT.vcd");

$dumpvars(0, FFT_IFFT_tb);

#2000 $finish();

end约 693 字大约 2 分钟

2025-01-08

仿真搭建的目的是帮助用户能快速搭建起自己的仿真框架,并快速的获得仿真结果。

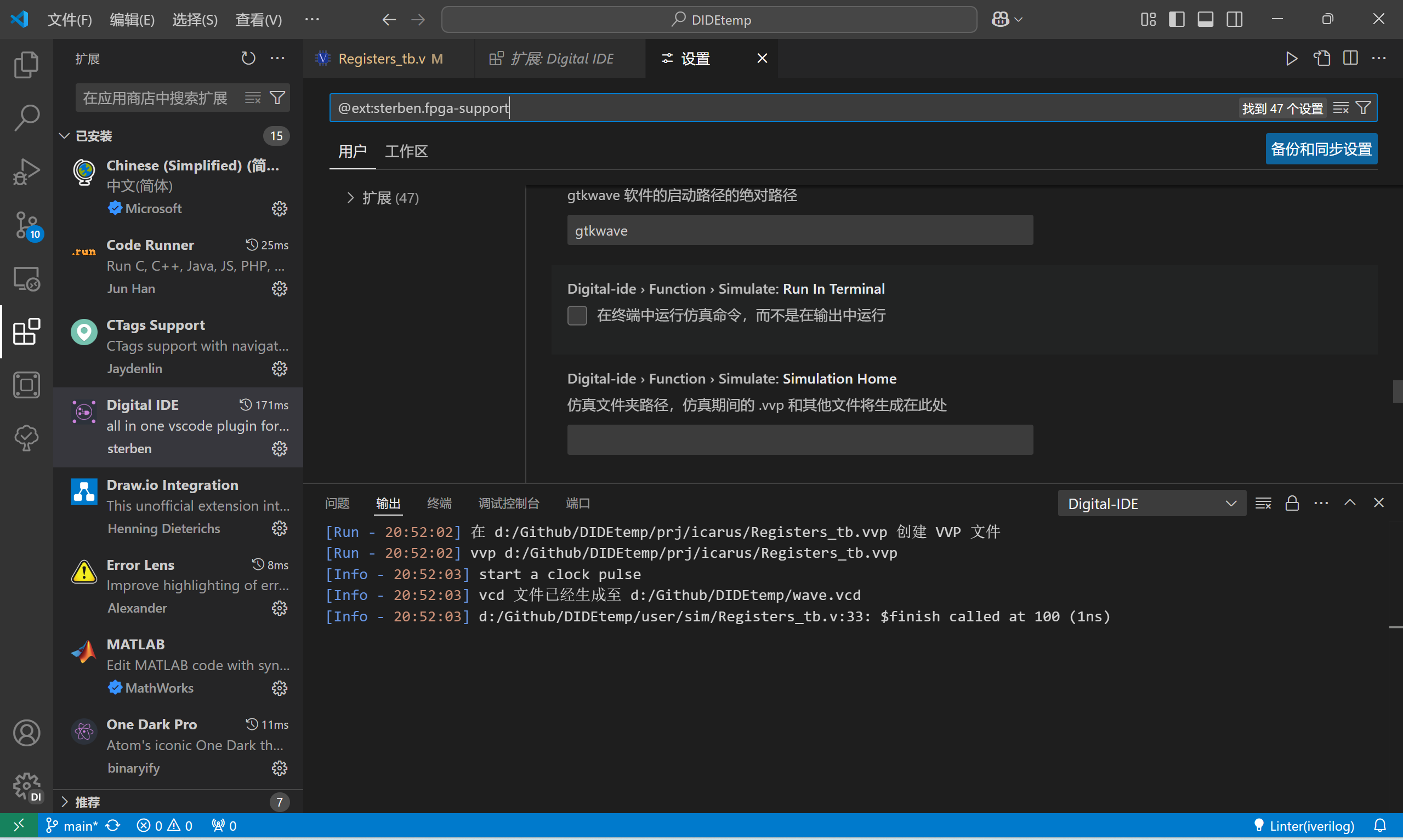

当前针对小模块的快速验证,我们给出了一个一键快速仿真的功能,该功能依赖的是iverilog来完成的。因此用户需要自己配置好iverilog的安装。

对于0.4.0最新版来说,我们对include做了专门的设计,无论写不写include都能正常仿真,但我们强烈不建议写include,include本身的设计会导致更高的复杂度,导致运行的不稳定性。

初期配置时,安装好iverilog,并将其配置到系统环境下,或者在setting中配置其安装路径。

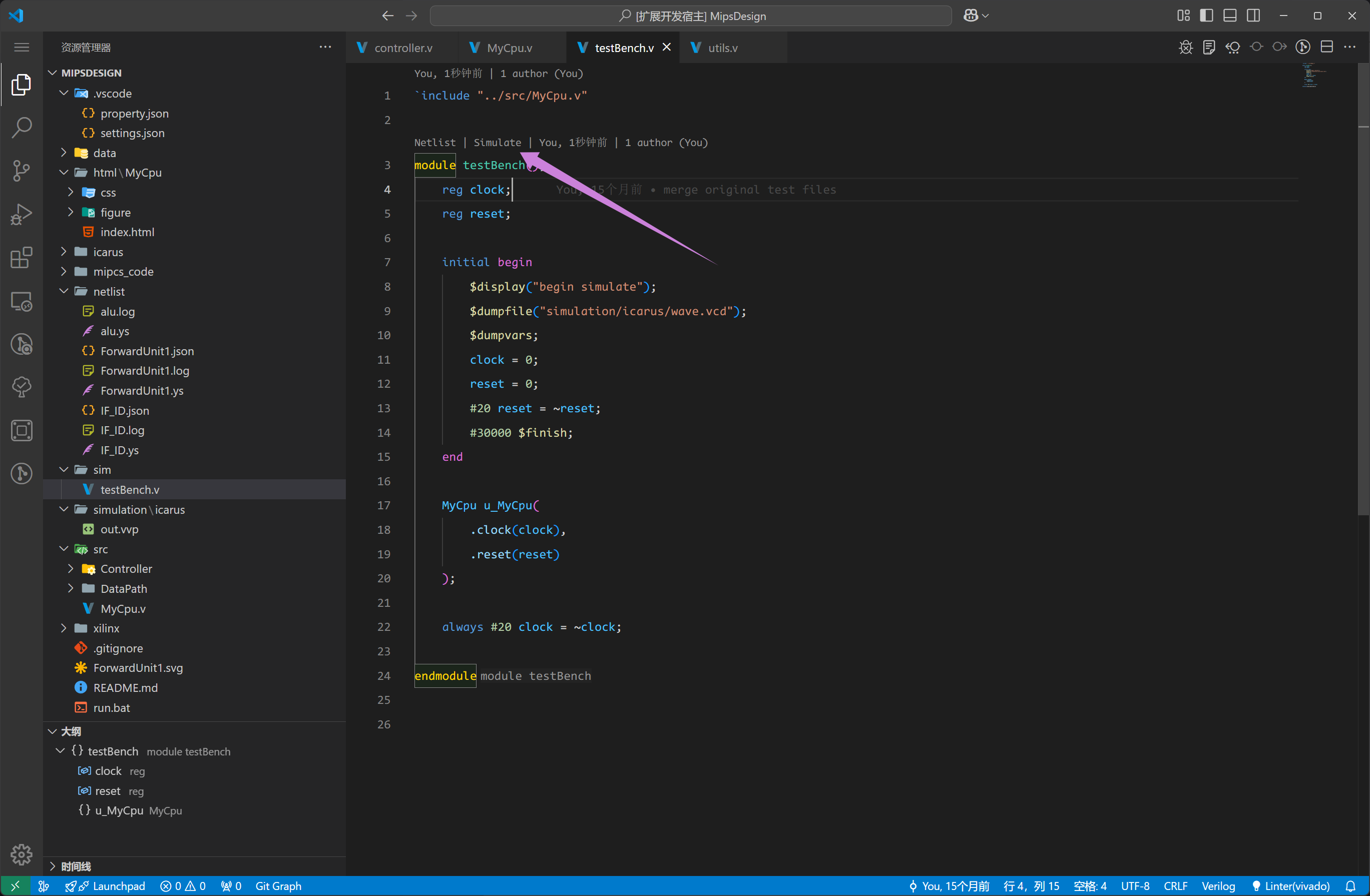

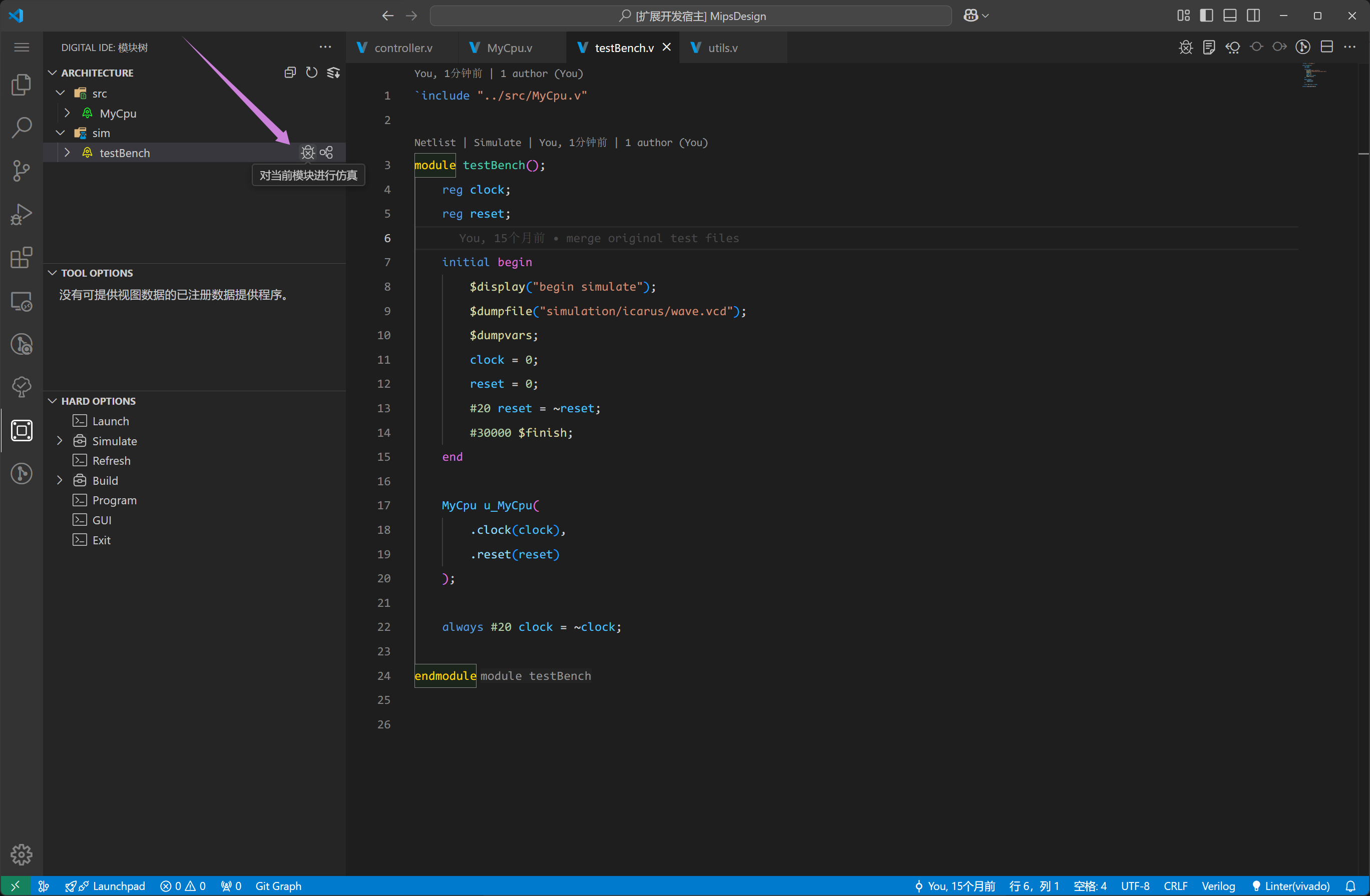

快速仿真的触发方式有两种。一种通过 codelens 的行间字符,一种通过模块树的按钮。

如下图所示的,悬浮在模块命名上的Simulate按键功能入口

如下图所示的依赖结构中的功能入口

点击快速仿真之后,如果生成了 vcd 文件, DIDE 会自动打开对应的波形渲染器:

没有生成 vcd 文件

没有生成 vcd 文件

如果运行的过程中没有报错,那可能是tb文件中缺少生成vcd波形文件的语句:

initial begin

$dumpfile("prj/icarus/FFT_IFFT.vcd");

$dumpvars(0, FFT_IFFT_tb);

#2000 $finish();

end 生成的 vcd 文件在哪里?

生成的 vcd 文件在哪里?

当你在项目中使用 dumpfile 指定导出路径时,这个路径的根路径是你的工作目录。比如对于下面的文件结构:

test.v 文件内容

module test();

initial begin

$dumpfile("prj/test.vcd");

#2000 $finish();

end

endmodule那么,生成的 vcd 就在根目录下的 prj/test.vcd 也就是下面这个文件结构:

直接卡死,毫无输出

直接卡死,毫无输出

如果运行的过程中没有报错,那可能是tb文件中缺少$finish();,强烈不建议这么做,这样做vcd会不断变大,后端iverilog也会卡住进程。需要在设计中加入一个$finish();来完善整个验证设计。

无法 simulate 且没有报错内容

无法 simulate 且没有报错内容

快速仿真功能报错时:

run in terminal